What is Global Integrated Circuits (IC) Packaging & Testing Market?

The Global Integrated Circuits (IC) Packaging & Testing Market is a crucial segment in the semiconductor industry, focusing on the final stages of semiconductor device fabrication. This market involves the encapsulation of integrated circuits into protective packages and the subsequent testing to ensure functionality and reliability. Packaging serves multiple purposes, including protecting the ICs from physical damage and environmental factors, facilitating electrical connections, and enabling thermal management. Testing, on the other hand, is essential to verify the performance and quality of the ICs before they are shipped to customers. The market is driven by the increasing demand for electronic devices, advancements in technology, and the need for miniaturization and enhanced performance of ICs. As electronic devices become more complex, the packaging and testing processes have evolved to accommodate smaller, more powerful chips. The market is characterized by continuous innovation, with companies investing in research and development to improve packaging materials, techniques, and testing methodologies. The growth of the Internet of Things (IoT), artificial intelligence (AI), and 5G technology further propels the demand for advanced IC packaging and testing solutions. The market is highly competitive, with key players striving to offer cost-effective and efficient solutions to meet the diverse needs of various industries.

in the Global Integrated Circuits (IC) Packaging & Testing Market:

The Global Integrated Circuits (IC) Packaging & Testing Market encompasses a variety of packaging types, each catering to specific customer requirements and applications. One of the most common types is the Dual In-line Package (DIP), which is widely used due to its simplicity and ease of handling. DIP packages are typically used in through-hole mounting applications and are favored for their robustness and reliability. Another popular type is the Surface Mount Technology (SMT) package, which includes various subtypes such as Small Outline Integrated Circuit (SOIC), Quad Flat Package (QFP), and Ball Grid Array (BGA). SMT packages are designed for surface mounting on printed circuit boards (PCBs) and are preferred for their compact size and ability to support high-density circuit designs. BGA packages, in particular, are known for their excellent thermal and electrical performance, making them suitable for high-performance applications. Chip Scale Packages (CSP) are another category, offering a near-die size package that is ideal for applications requiring minimal space. CSPs are commonly used in mobile devices and other portable electronics where size and weight are critical factors. Wafer Level Packaging (WLP) is an advanced packaging technology that involves packaging the ICs at the wafer level, allowing for reduced package size and improved electrical performance. WLP is increasingly used in applications such as smartphones and wearable devices. Additionally, there are specialized packages like Multi-Chip Modules (MCM) and System-in-Package (SiP), which integrate multiple ICs and passive components into a single package. These are used in complex applications requiring high levels of integration and functionality. The choice of packaging type depends on various factors, including the intended application, performance requirements, cost considerations, and manufacturing capabilities. Customers in the automotive industry, for example, may prioritize packages that offer high reliability and resistance to harsh environmental conditions, while those in the consumer electronics sector may focus on size and cost efficiency. The testing aspect of the market is equally diverse, with various testing methodologies employed to ensure the quality and performance of the packaged ICs. Functional testing, parametric testing, and burn-in testing are some of the common testing techniques used to identify defects and verify the functionality of the ICs. The testing process is critical to ensure that the ICs meet the required specifications and can operate reliably in their intended applications. Overall, the Global Integrated Circuits (IC) Packaging & Testing Market is characterized by a wide range of packaging types and testing methodologies, each tailored to meet the specific needs of different customers and applications.

Analog IC Packaging & Testing, MPU & MCUs IC Packaging & Testing, Logic IC Packaging & Testing, Memory IC Packaging & Testing in the Global Integrated Circuits (IC) Packaging & Testing Market:

The usage of Global Integrated Circuits (IC) Packaging & Testing Market spans across various areas, each with its unique requirements and challenges. In the realm of Analog IC Packaging & Testing, the focus is on ensuring the precision and reliability of analog signals. Analog ICs are used in a wide range of applications, including audio processing, power management, and sensor interfaces. The packaging for analog ICs must provide excellent thermal management and electromagnetic interference (EMI) shielding to maintain signal integrity. Testing for analog ICs involves verifying the accuracy and linearity of the signals, as well as ensuring the ICs can operate under various environmental conditions. In the case of MPU & MCUs IC Packaging & Testing, the emphasis is on performance and integration. Microprocessor Units (MPUs) and Microcontroller Units (MCUs) are the brains of many electronic devices, from computers to household appliances. The packaging for MPUs and MCUs must support high-speed data processing and efficient power management. Testing for these ICs involves assessing their computational capabilities, power consumption, and response to different input conditions. Logic IC Packaging & Testing focuses on digital circuits that perform logical operations. Logic ICs are fundamental components in digital systems, used in everything from simple logic gates to complex processors. The packaging for logic ICs must accommodate high-speed signal transmission and minimize signal delay. Testing for logic ICs involves verifying the correctness of logical operations and ensuring the ICs can handle the required data throughput. Memory IC Packaging & Testing is centered around data storage and retrieval. Memory ICs, such as DRAM, SRAM, and Flash, are critical for storing data in electronic devices. The packaging for memory ICs must provide high-density storage and fast access times. Testing for memory ICs involves checking for data retention, read/write speeds, and error rates. Each of these areas within the Global Integrated Circuits (IC) Packaging & Testing Market requires specialized packaging and testing solutions to meet the specific demands of the applications they serve.

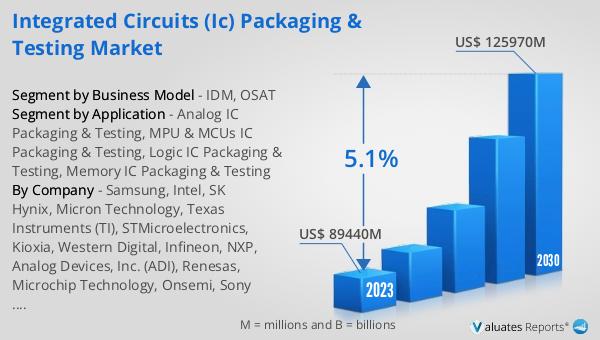

Global Integrated Circuits (IC) Packaging & Testing Market Outlook:

In 2024, the global market for Integrated Circuits (IC) Packaging & Testing was valued at approximately $93,730 million. This market is anticipated to expand significantly, reaching an estimated size of $131,700 million by 2031, reflecting a compound annual growth rate (CAGR) of 5.1% over the forecast period. Despite being the largest region, Asia Pacific experienced a decline of 2.0 percent. Meanwhile, the Americas saw a substantial increase in sales, amounting to $142.1 billion, which represents a 17.0% year-on-year growth. Similarly, Europe experienced a notable rise in sales, reaching $53.8 billion, marking a 12.6% increase compared to the previous year. Japan also saw an upward trend, with sales totaling $48.1 billion, up by 10.0% year-on-year. However, the Asia-Pacific region, despite being the largest market, reported sales of $336.2 billion, which was a decrease of 2.27% year-on-year. These figures highlight the dynamic nature of the global IC Packaging & Testing market, with varying growth rates across different regions. The market's expansion is driven by the increasing demand for advanced electronic devices and the continuous evolution of semiconductor technologies.

| Report Metric | Details |

| Report Name | Integrated Circuits (IC) Packaging & Testing Market |

| Accounted market size in year | US$ 93730 million |

| Forecasted market size in 2031 | US$ 131700 million |

| CAGR | 5.1% |

| Base Year | year |

| Forecasted years | 2025 - 2031 |

| Segment by Business Model |

|

| Segment by Application |

|

| By Region |

|

| By Company | Samsung, Intel, SK Hynix, Micron Technology, Texas Instruments (TI), STMicroelectronics, Kioxia, Western Digital, Infineon, NXP, Analog Devices, Inc. (ADI), Renesas, Microchip Technology, Onsemi, Sony Semiconductor Solutions Corporation, Panasonic, Winbond, Nanya Technology, ISSI (Integrated Silicon Solution Inc.), Macronix, Giantec Semiconductor, Sharp, Magnachip, Toshiba, JS Foundry KK., Hitachi, Murata, Skyworks Solutions Inc, Wolfspeed, Littelfuse, Diodes Incorporated, Rohm, Fuji Electric, Vishay Intertechnology, Mitsubishi Electric, Nexperia, Ampleon, CR Micro, Hangzhou Silan Integrated Circuit, ASE (SPIL), Amkor, JCET (STATS ChipPAC), Tongfu Microelectronics (TFME), Powertech Technology Inc. (PTI), Carsem, King Yuan Electronics Corp. (KYEC), SFA Semicon, Unisem Group, Chipbond Technology Corporation, ChipMOS TECHNOLOGIES, OSE CORP., Sigurd Microelectronics, Natronix Semiconductor Technology, Nepes, Forehope Electronic (Ningbo) Co.,Ltd., Union Semiconductor(Hefei)Co., Ltd., Hefei Chipmore Technology Co.,Ltd., HT-tech, Chippacking |

| Forecast units | USD million in value |

| Report coverage | Revenue and volume forecast, company share, competitive landscape, growth factors and trends |